RISC-Vの誕生 既存の命令セットアーキテクチャでは満足できなかった、その理由:RISCの生い立ちからRISC-Vまでの遠い道のり(1/3 ページ)

やっと、IBM 801からRISC-Vまで話がたどり着いた。RISC-Vの生い立ちについては以前EETimesで記事を書かせていただいたが、改めて簡単にご紹介を。

昨今の大学の場合、CPUを設計する、というのは割とごく一般的なもの「らしい」(筆者は地方大学の理学部物理学科出身なので、いまいち情報系とか計算機系の研究室のカリキュラムがよく分かっていない)。例えば東京大学理学部の情報科学科では、学部の3年生になるとCPUを作るという課題が与えられるそうだ。ターゲットはFPGAボードであるが、この上で自分の考えたアーキテクチャのCPUをHDL(Hardware Description Language:ハードウェア記述言語)で記述する形で実装し、さらにこのCPUの上で動くコンパイラも自作して、課題のアプリケーション(レイトレーシングによるCG作成、だそうだ)をコンパイル・実行してその実行速度を競うというものである。別に東大だけの話ではなく、海外でも特に情報系あるいはコンピュータ学科などでは、こうした「自身でCPUを作る」といったカリキュラムはごく一般的にある。

それもあって、例えばArmは2013年からUniversity Programを開始して、Cortex-M0のRTLの無償提供を行ったりしていた。現在はこれがDesignstart for Universityに進化している。これとは別にArm University Program Education Kitsなどのプログラムもあるが、いずれにせよArmのIPを無償で使える、またはArmベースのシリコンを無償で使える「だけ」のプログラムであり、そのIPの中身の教育には使えない。

先の例でいえば、CPUを自分で作るカリキュラムの前段階として、「通常CPUの中身はこんな風に作られる」といった授業の教材には使えないことになる。あるいは、研究プロジェクトの中で命令セットを書き換えるとか細工をしてみたい、といった用途にも当然使えない。

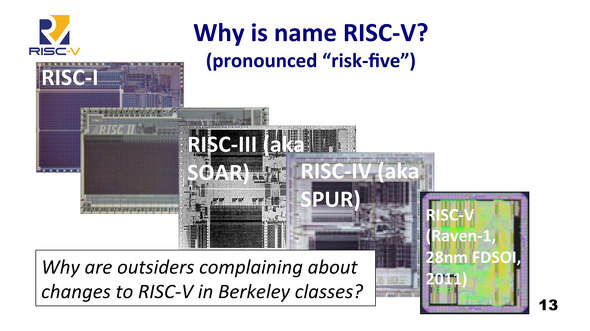

RISC-Vの生みの親であるであるUC Berkeley(米カリフォルニア大学バークレー校)のカーステ・アサノビッチ教授が直面していたのがまさにこの状況である。教授は2010年から“Resiliency for Extreme Energy Efficiency”という、超低消費電力で動作するプロセッサの研究プロジェクトを行っており、この目的で2011年に「Raven-1」というプロセッサが開発された(写真1)。

Raven-1そのものは28nmの完全空乏型シリコン・オン・インシュレータ(FD-SOI)で製造され、最終的に26.2GFlops/Wという高い性能/消費電力比を達成している。ちなみに今年のTOP500の最上位である富岳でも41万5530TFlops/2万8335KWで14.66GFlops/Wでしかない。Green500でトップになったPreferred NetworksのMN-3でも21.11GFlops/Wであり、実験的なプロセッサとはいえ、2011年に26GFlops/W以上の性能を実現したという点で、Raven-1(研究プロジェクト)は成功だったわけだが、話はここからである。

そもそもBerkeleyではいくつもプロセッサが作られた。RISC-I(Berkeley RISC)と、これを改良したRISC-IIはデビッド・パターソン教授の指揮の下、1981~82年に開発された。

このRISC-IIをベースにSmalltalkを搭載したのが1983年~1984年に開発された「SOAR」(Smalltalk On A RISC)である。SmalltalkはPARC(Xeroxのパロアルト研究所)で開発されたプログラミング言語だ。もともとはXeroxのAltoというマシンのOS的な位置付けだったのが、紆余曲折あって1980年に「Smalltalk-80」というプログラミング言語(統合開発環境というべきかもしれない)として1983年に発売された(Smalltalk-80 version 2)が、これに先立ちいくつかの会社とUC Berlekeyには初期バージョン(Smalltalk-80 version 1)が提供された。

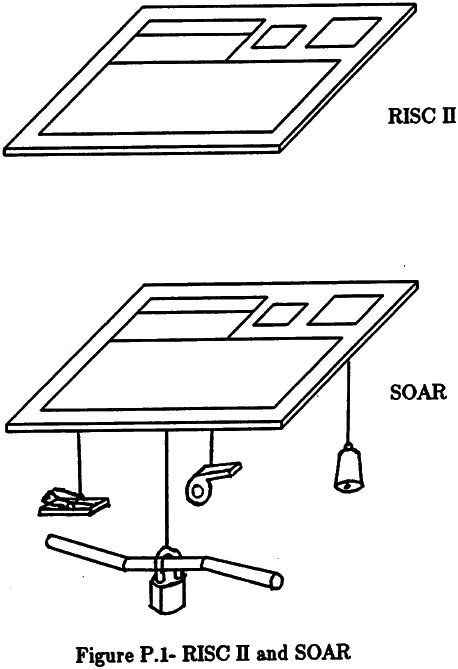

SOARはどうもこのSmalltalk-80 version 1を動かすために開発されたプロセッサだったようだ。ベースとなるのはRISC-IIそのものであるが、RISC-IにしてもRISC-IIにしても、想定していたのはC言語であり、Smalltalk向けではなかった。それもあってSmalltalk向けに、さまざまな命令トラップやマルチサイクル命令のハンドリングなどを加えたのがSOARだった模様(写真2)。

写真2:RISCのコンセプトからすると、SOARで追加したものは明らかに「余分なもの」だったのだろうが、Smalltalkの実行にはこうしたものがあった方が便利だった、ということを、なんともいえない表現で示している。出典はジョーン・マリー・ペンドルトン博士の“A Design Methodology for VLSI Processors”(PDFへのリンク)

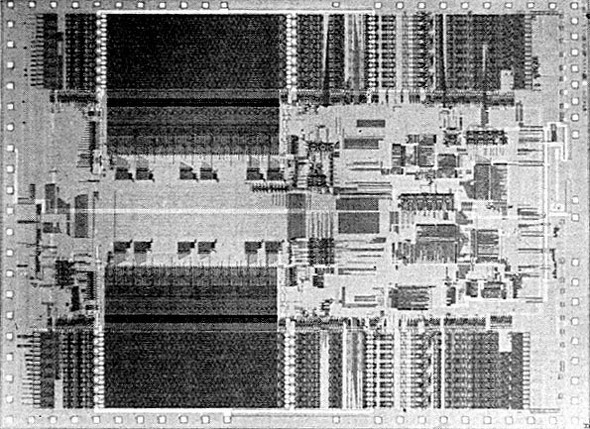

写真2:RISCのコンセプトからすると、SOARで追加したものは明らかに「余分なもの」だったのだろうが、Smalltalkの実行にはこうしたものがあった方が便利だった、ということを、なんともいえない表現で示している。出典はジョーン・マリー・ペンドルトン博士の“A Design Methodology for VLSI Processors”(PDFへのリンク)このSOARは4μmのNMOSプロセスで作成され、3万5700トランジスタで構成されている。400nsのサイクル時間で動作し、消費電力は3Wだったとされている(写真3)。

写真3:SOARのダイ写真。いろいろ手を入れたとはいえ、基本的にはRISC-IIの延長にあるため、ダイのレイアウトもよく似ている。出典は“Berkeley Hardware Prototypes”(PDFへのリンク)

写真3:SOARのダイ写真。いろいろ手を入れたとはいえ、基本的にはRISC-IIの延長にあるため、ダイのレイアウトもよく似ている。出典は“Berkeley Hardware Prototypes”(PDFへのリンク)実はこのSOAR、UC Berkeleyの授業として学生のグループにより設計・製造されたものだった(写真4)。論文の著者であるペンドルトン氏もこの授業に参加してSOARの設計に携わったとされている。経歴を見ると、彼女はこのSOARの設計で博士号を取得したようだ(指導教官は当然ながらデビッド・パターソン教授である)。

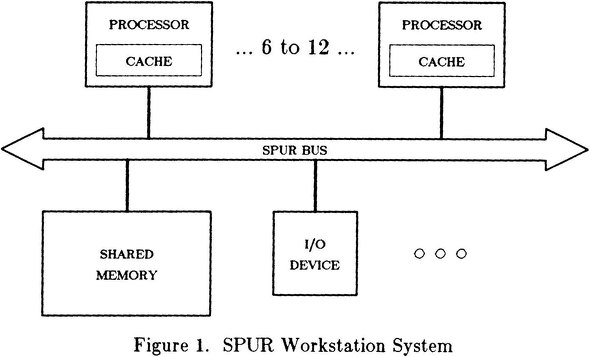

Berkeleyで作られた4つ目のプロセッサがSPURであるが、現在のUC BerkeleyのSPUR(Sponsored Projects for Undergraduate Research)とは何の関係もない。「SPUR」とはSymbolic Processing Using RISCsの略で、Parallel Processingの研究プロジェクトの一環である。このプロジェクト、DARPA(米国防高等研究計画局)がスポンサーになっており、その意味では研究費用は潤沢にあったようだ。Parallel Processingというのは要するにマルチプロセッサ構成(写真5)という意味で、最大12プロセッサからなる、ワークステーション向けの構成である。

写真5:SPUR BusはTIのNuBusをベースに若干カスタマイズを行ったものだったそうだ。出典は“SPUR:A VLSI Multiprocessor Workstation ”(PDFへのリンク)

写真5:SPUR BusはTIのNuBusをベースに若干カスタマイズを行ったものだったそうだ。出典は“SPUR:A VLSI Multiprocessor Workstation ”(PDFへのリンク)Copyright © ITmedia, Inc. All Rights Reserved.

Special

PR